Resolvi escrever este post, ao qual vai acompanhado um vídeo no meu canal no Youtube, para esclarecer dúvidas que muitos técnicos ainda têm sobre os Transistores de Efeito de Campo, conhecidos pela sigla, em inglês, FET que significa Field Effect Transistor.

A maioria dos livros, senão todos, gastam muitas páginas analisando a física dos semicondutores o que finda por tornar o assunto cansativo e até, porque não dizer, incompreensivo e inútil deixando de tratar objetivamente o que interessa, principalmente, a um técnico reparador, que é saber como funcionam estes componentes, seus principais parâmetros e como testá-los.

Para o reparador, que é o foco do meu trabalho, saber como os FETS funcionam é importante para poder testá-los.

Por outro lado, conhecer os principais parâmetros, torna-se cada vez mais necessário na hora de fazer uma substituição, mas sobre isto eu trato com detalhes no meu e-book Diodos & Transistores Procurando Substitutos.

Temos no mercado uma enorme quantidade de equipamentos para os quais não encontramos peças originais para substituição, uma vez que os fabricantes, mesmo quando “oficialmente” instalados no Brasil, dificultam o reparo ao máximo, daí a necessidade de o técnico entender os parâmetros dos semicondutores para saber se o componente que encontra no mercado paralelo, com um código diferente do que procura, atende à substituição e, além disso, não é falsificado.

A família dos FETs

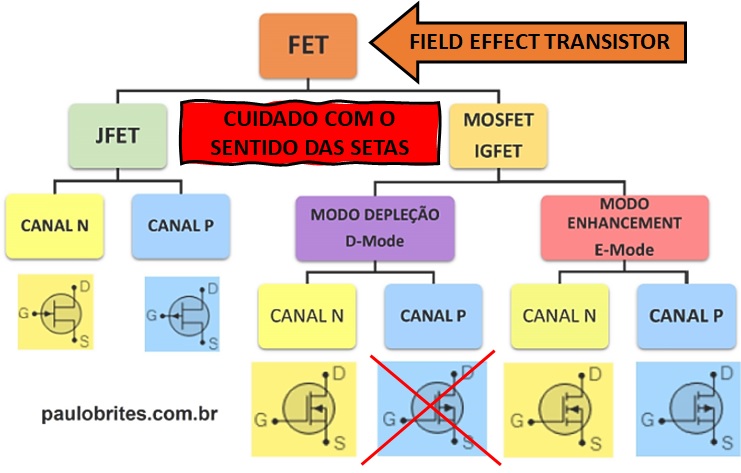

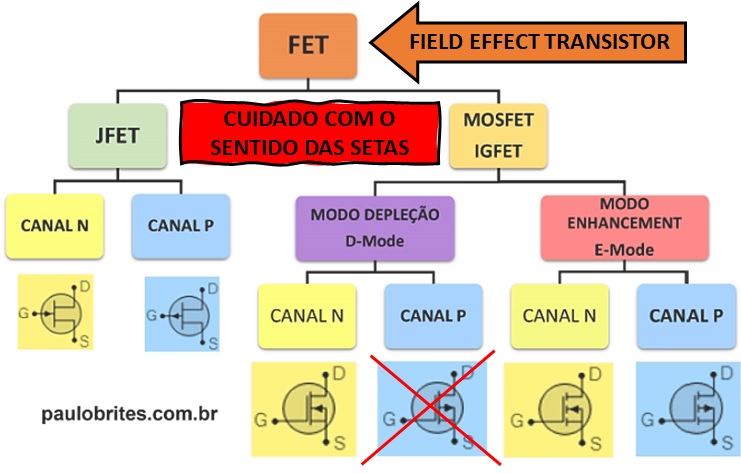

Comecemos dando uma olhada no painel da fig.1 que extraí do meu e-book Fontes Chaveadas para Principiantes Volume 1.

Fig. 1 – Família dos FETs

Observe no gráfico da fig.1 que a “família” dos FETs se divide em dois grupos principias.

À esquerda temos os JFETs que são os FETs de Junção fabricados com duas tecnologias designadas por Canal N e Canal P.

Do lado direito temos os MOSFETs, sigla para Metal Oxide Silicon Field Effect Transistor, também chamados IGFET que significa Insulated Gate FET.

Eu, particularmente, prefiro IGFET, embora quase não se use esta denominação.

A sigla IGFET expressa a tecnologia utilizada na fabricação – FET de Porta Isolada e os diferencia dos JFETS que são FETs de Junção.

Voltado a fog.1 e olhando o lado direito do gráfico podemos observar que os MOSFETs além de se apresentarem como Canal N e Canal P, se subdividem em Modo Depleção (D-Mode) e Modo Enhancement (E-Mode), termo que costuma ser traduzido como Enriquecido ou Melhorado.

Certamente, para muitos que estão a ler este artigo, os termos Modo Depleção e Modo Enhancement são uma novidade portanto, irei explicar o que significa cada um deles e qual a importância de saber as diferenças entre os dois.

O que significa depleção?

Este é um termo oriundo da biologia, mais especificamente da medicina e expressa a perda ou diminuição de uma substância armazenada num organismo ou órgão.

E o que isso tem a ver com os FETs?

Deixo, momentaneamente, esta curiosidade corroendo seus miolos, mas afirmo que quando você entender como um JFET funciona ficará fácil descobrir por que os físicos, que inventaram este tipo de transistor, usaram o termo depleção para definir seu modo de operação.

Diferença entre a construção de um BJT e um JFET

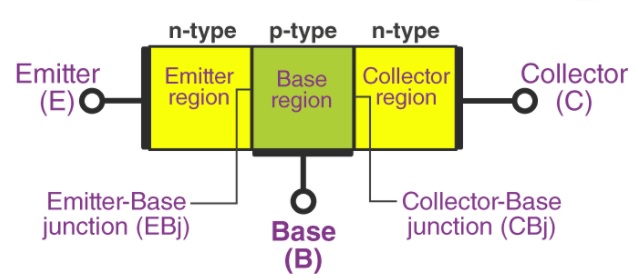

O termo “correto” para designar os transistores “usuais”, conhecidos como NPN e PNP, é BJT que significa Bipolar Junction Transistor onde Junction está associado as junções de semicondutores tipo N e tipo P e, obviamente, como são duas com polaridades diferentes, N e P, usa-se o termo bipolar.

A fig. 2 mostra a estrutura das duas junções de um transistor BJT NPN apenas ilustrar o que foi dito.

Fig. 2 -Estrutura de um BJT NPN

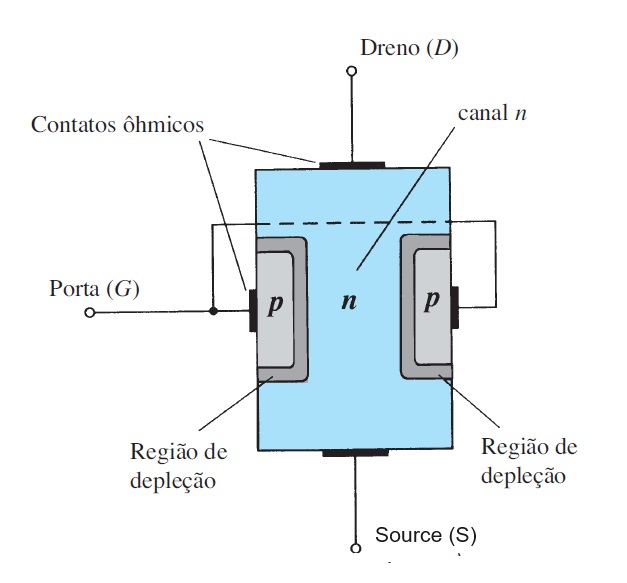

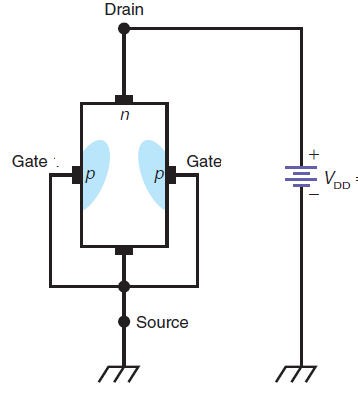

Agora, acompanhe na fig.3 como é a estrutura de um JFET, de forma simplificada pois, como eu disse no início, não vejo necessidade de aprofundar na física dos semicondutores.

Fig. 3 – Estrutura do JFET Canal N

Temos uma barra de semicondutor, neste caso, tipo N, denominada CANAL, com dois terminais: source e dreno.

O terminal source costuma ser traduzido como fonte, mas eu prefiro chamá-lo de supridouro para que não seja confundido com “fonte de alimentação”.

Observando a fig. 3 vemos uma região de semicondutor tipo P “introduzida” no canal N.

Um terminal de contato é ligado a este semicondutor tipo P e será denominado de GATE, que é traduzido por PORTA.

Na fig. 3, vemos também uma região em torno do semicondutor P que é denominada por depleção cuja função é diminuir o fluxo de cargas no canal o que é compatível, usando um pouco de imaginação, com a “definição”, oriunda da medicina, dada anteriormente.

Polarizando um JFET – Importante saber isso

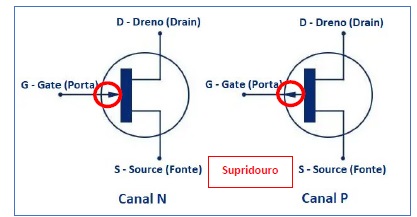

Antes de mostrar como se polariza um JFET, vale a pena fazer dois comentários sobre e simbologia utilizada para os JFETs que vai mostrada na fig. 4.

Fig. 4 – Simbologia dos JFETs

Observe o sentido da seta que representa o terminal do GATE.

Para o JFET canal N a seta aponta para dentro, enquanto no canal P ela aponta para fora.

Cuidado para não confundir com o sentido utilizado nos transistores BJT.

A segunda observação é quanto a maneira como se representa a “ligação” entre o terminal supridouro (source) e o dreno, que é feita por uma linha continua.

Observe, na fig. 1, que na simbologia dos MOSFETs Modo Enhancement está linha é pontilhada.

Você saberia dizer por que a diferença? Pense nisso.

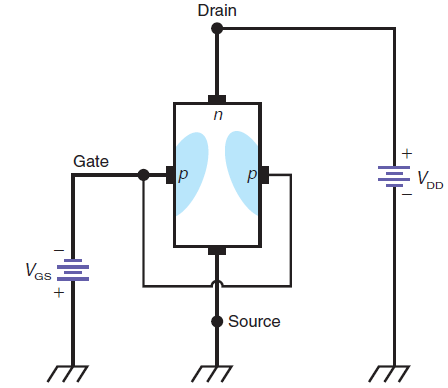

Enquanto você vai tentado descobrir a diferença entre a linha continua e pontilhada na simbologia dos MOSFETs vamos dar uma olhada nas figuras 5 e 6 para ver como se polariza um JFET.

Fig. 5 – JFET Canal N com Tensão Gate-Source igual a zero

Para o Canal N a tensão entre Dreno e Source deve ser aplicada como mostrada na Fig. 5, com o Dreno positivo em relação a Source.

Se for Canal P VDD e VGG deverão ser invertidas.

Com a tensão VGS nula (fig.5) teremos o máximo de circulação de corrente no canal que aparece no data sheet como IDSS.

Se quisermos diminuir a corrente no canal devemos aplicar uma tensão negativa no gate em relação a source como mostra a fig.6 para o canal N.

Basicamente os terminais Gate-Source atuam como se formassem um diodo portanto, neste caso, não devem ser polarizados diretamente.

Quanto mais negativa for VGS maior será a região de depleção o que provoca o estreitamento do Canal e a diminuição da corrente ID.

Por que é importante saber isso?

Quando vamos testar um JFET precisamos ter cuidado para nunca polarizar o gate diretamente em relação a source, pois corremos o risco de danificar o transistor.

Iremos ver isto com mais detalhes quando formos utilizar o DY-294 para testar JFETs.

Pontos importantes sobre os MOSFETs

Como vimos na fig.1 estes tipos de FETS podem ser fabricados para operar em dois modos: depleção ou Enhancement.

Os JFETs só operam no modo depleção.

Na prática os D-MOSFETs são raros e se for canal P, mais ainda por isso, não irei me dedicar, no momento, a estudá-los.

Por ora, basta saber, se você encontrar um D-MOSFET por aí, que eles se comportam de maneira semelhantes aos JFETs exceto pelo fato de terem impedância de entrada muito mais alta uma vez que a porta está isolada do canal.

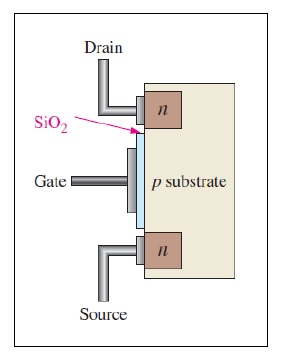

Comecemos dando uma olhada na fig. 7, onde temos a estrutura de um E-MOSFET canal N, para que você entenda a diferença entre o modo depleção e o modo enchachement.

Fig. 7 – Estrutura de um E-MOSFET Canal N

A primeira coisa a se observar na fg.7, a qual mostra a estrutura do E-MOSFET, é que não há uma “ligação direta” entre o dreno e o supridouro (source) como ocorre no D-MOSFET (reveja a fig.3).

E o que isto significa?

Significa que se não tivermos polarização entre gate e source não haverá corrente de dreno, em outras palavras, os E-MOSFETs funcionam com uma chave normalmente aberta.

Da afirmação acima podemos tirar duas conclusões imediatas.

A primeira refere-se a linha pontilhada na simbologia dos E-MOSFETs indica justamente que não há uma “ligação direta” entre dreno e source.

A segunda conclusão é mais sútil e explica por que os E-MOSFETs são utilizados nas fontes chaveadas.

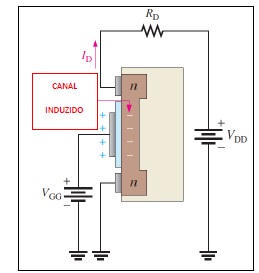

Finalmente, faltou dizer que também não há uma “ligação direta” entre o gate e o semicondutor tipo P, neste caso, em que o temos um E-MOSFET canal N. Este semicondutor tipo P é denominado substrato e sua função é induzir um canal entre source e dreno como vemos na fig. 8.

Fig.8 – Canal Induzido no substrato

Entre o gate e o substrato temos uma camada de óxido de silício (SiO2) que o mantém isolado do canal e assim, a transferência de carga ocorre capacitivamente, por isso se não tivermos polarização no gate não haverá corrente no canal.

Polarizando o E-MOSFET

Diferentemente dos D-MOSFET que conduzem o máximo de corrente de dreno (IDSS) quando a tensão gate-supridouro é nula, os E-MOSFETs ficam cortados se VGS = 0V.

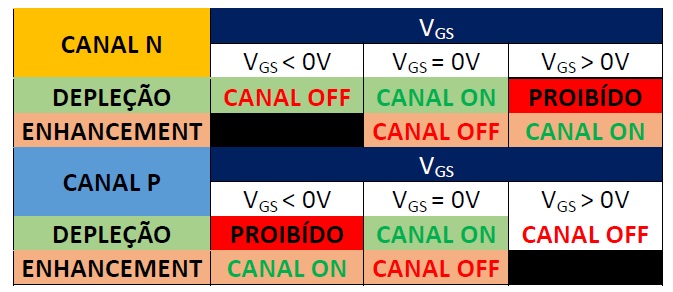

A tabela a seguir ilustra o que acontece com a tensão aplicada entre gate e source para cada canal e modo de operação.

Analisando com atenção a tabela acima alguns pontos importantes devem ser observados:

- Como os JFETs só operam no modo DEPLEÇÃO eles sempre conduzem para VGS = 0V.

- Não podemos ter polarização direta entre gate-source nos JFETs, pois eles só operam no modo DEPLEÇÃO.

- Os MOSFETs, que operam no modo Enhacement, sempre ficam cortados para VGS = 0V e por isso, são utilizados em fontes chaveadas.

Os pontos que foram analisados aqui serão demonstrados praticamente no vídeo a seguir.

Eu comprei um Transistor como BF245C mas recebí um BF245B, o pinout de ambos é diferente, posso simplesmente ligar conforme o pinout do BF245C correspondente, minha pergunta é funciona?

Agradeço suas explicações.

Luiz Alberto, olhe no data sheet se há defensas relevantes nas especificações elétricas. Em princípio pode funcionar obedecendo a pinagem correta e se o transistor não for falsificado. Já comprei FET que na verdade erar um BJT carimbando com o código de um FET.

Sou um dos que tenho acompanhado sua maneira objetiva de explicar eletrônica . Acho que sou um dos mais antigos técnicos, que ler sempre suas informação de eletrônicas …. pois já tenho (91) anos de idade e comecei a estudar eletrônica em fortaleza , com 15 anos de idade ( naquela época os autofalantes eram campo magnéticos de bobinas !)

Caro Edmilson, que prazer ler seu depoimento.

Eu sou jovem a menos tempo, caminhando para os 80, no ano que vem.

Também comecei lá pelos 15 e pequei estes alto falantes. A bobina servia com choque de filtro para a fonte.

Forte abraço e até sempre!